24小时联系电话:18217114652、13661815404

中文

技术专题

层之间的PCB间隙和走线间距规则

大多数设计人员习惯在同一层上走线之间的PCB间隙规则。但是,层之间的PCB间隙是设计中经常被忽略的因素。但是,如果您十年前从事该行业,那么您可能就不必担心了。

如果您现在正在进行电路设计,则不能说相同的话。如今,单电源设计在同一基板上存在电源和控件的情况已变得越来越普遍。尽管这样做的风险是在低压信号附近有高压走线。

当两个电位差很大的导体彼此靠近放置时,就有发生电弧的危险。换句话说,火花可能会通过绝缘层跨过高压走线到达信号走线。瞬间,低压组件的端口可能会遭受灾难性损坏。

如果您在PCB上的电压为30VAC或60VDC及以上,则应该研究各层之间的走线间隙。同样,在描述高压导体之间的分隔时,术语“爬电”而不是“间隙”更为准确。

电气间隙是指暴露于空气中沿直线测量时导体之间的距离。同时,爬电距离是指在绝缘材料的表面上测量时导体之间的距离。

规范PCB电气间隙的标准

尽管通常讨论相似层上的迹线之间的间隙,但很少提及将迹线放在不同层上时将它们分开。在这件事上,PCB设计者可以参考任何标准吗?是!

IPC2221B

IPC2221B是PCB设计中的通用参考标准。它可能涵盖设计过程的每个方面,包括电气间隙。

在其中,您将能够发现有关板形状,轮廓和安装孔的各种设计思想的必要间隙。影响制造限制的电路板形状,确定电路板和组件的机械支撑或连接的安装孔以及确定放置和组装能力的轮廓都可能影响间隙的决定。考虑可以将您的组件放置得多么紧密,以实现最佳的可制造性。

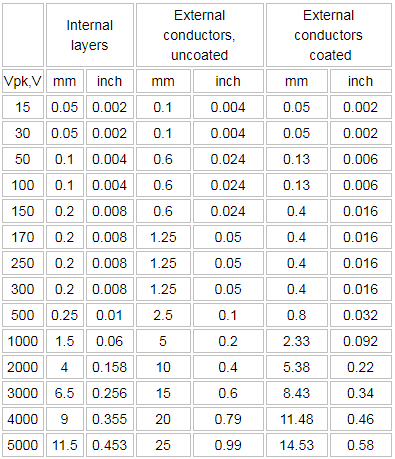

您可以在表6.1中找到PCB之间间隙的特定值。B1列显示内部导体之间的间距值:

高压走线应如何在层之间分开?

防止高压信号走线与低压信号过于接近的最佳方法是不要将它们放在同一PCB上。但是,随着现代产品变得越来越紧凑,对于某些人来说,这被证明是不可能的选择。

与同一层上的迹线分隔不同,您的选择非常有限。您不能通过添加插槽或对迹线之间的绝缘区域进行v刻痕来增加爬电距离。任何实际的调整都是增加分隔迹线的衬底的厚度。

因此,IPC-2221B可作为在中间层分隔导体的预浸料厚度的良好参考。例如,对于100V的走线,您需要0.1 mm的间距。

另外,您将要考虑所用PCB的比较跟踪指数(CTI)。CTI是施加电压时材料击穿点的指示性测量。CTI的范围从0到5,最低的数字表示最坚固的材料。

FR4通常用于PCB,属于CTI值为175V至249V的类别3。如果使用更高的电压,则使用具有更高CTI值的PCB材料是有意义的。