24小时联系电话:18217114652、13661815404

中文

行业资讯

管理互连密度和信号噪声

经验丰富的PCB设计人员,那么您将了解“ 3W”规则,该规则规定走线之间的间距应始终至少为每条走线宽度的3倍。这个过时的规则并没有说明您的叠层或环路电感,但许多设计师仍然坚持使用此规则。随着HDI板被推向更小的尺寸和更高的密度,例如在具有6 mil迹线的基带芯片中,迹线之间的串扰和互连噪声耦合的强度将取决于它们之间的间距。这意味着您需要一种方法,以根据互连密度快速评估电路板中的串扰和EMI磁化率。

在设计PCB时,需要执行这些仿真并分析布局后的情况。换句话说,原理图编辑器无法考虑走线和组件的物理布局,因此不能用于模拟与堆栈,走线大小或走线密度有关的任何事情。原理图编辑器中的电路仿真器仍然在电路仿真中占有一席之地,但是管理互连密度需要直接从布局数据确定噪声耦合。

电路板将需要平衡许多不同的几何要求,以防止单端和差分走线之间发生串扰。高密度板上的困难仅是因为当您靠近走线时,走线发出的电磁场会更强。宽带信号的低频部分将(通过磁场)感应耦合到附近的迹线,而宽带信号的高频部分(通过电场)将感应耦合到附近的迹线。

相声

在管理互连密度时,您需要考虑不同类型的信号如何相互耦合。单端和差分对以各种方式与其他类型的走线耦合,下表显示了信号完整性仿真所期望的结果摘要。请注意,在单端→差分对串扰结果中,共模噪声或差分模式噪声的存在取决于受害差分对(S)中走线之间的间隔值以及该对离地线对的高度( H)。

|

攻击者信号类型 |

受害者信号类型 |

串扰特性 |

|

单端 |

单端 |

单端FEXT和NEXT随着间距增大而变弱。这是3W规则的由来。 |

|

差分对 |

串扰在很小和很大的间距下均以共模噪声为主,而差模噪声则以中频间隔(当S / H = 0.5时)为主。 |

|

|

差分对 |

单端 |

单端FEXT和NEXT随着间距增大而变弱。 |

|

差分对 |

当S很小时,串扰最大,随着S的增加,串扰消失。 |

在上表中,我们假设所有单端走线和差分对都位于同一层上(即,没有宽边耦合)。这是在大多数布局中需要模拟的常见情况。较宽的差分对是较不常见的布置,当并排放置时,它们会产生强烈的串扰。在所有情况下,差分对之间的串扰将比可比的单端走线之间的串扰弱,并且随着分离距离的增加,串扰强度将变弱。

由于市售数字电路的上升时间,在大多数数字系统中,鉴于相关信号上升时间,您的走线电感将主导串扰。但是,每个人都应该期望信号上升时间会继续下降,以适应更高数据速率的通道(例如800G和更高的SerDes),这可能会将有用的信号带宽推近100 GHz。有时,系统中需要考虑电容性串扰和电感性串扰。

量化EMI

相同的几何约束也将影响电路板对外部EMI的敏感性。电路板上信号走线的电感决定了它们对外部EMI的敏感性。电感耦合EMI产生于外部源的磁场,该磁场可能是宽带信号。外部EMI源(例如系统中的另一块板)会在不连续的峰值处强烈发射。隔离不良的时钟和高电流开关电源就是最好的例子。

EMI耦合为电路板中单端和差分网络上的共模噪声。耦合到走线中的噪声然后可以通过线性或非线性分量传播,然后可以以更高的谐波生成噪声。感应噪声和信号完整性之间的复杂反馈可能很难方便地模拟。但是,您的目标应该是通过最小化电路板上关键网络中的环路电感来最小化EMI。

模拟EMI和串扰与互连密度

您可以在完成布局之前或之后创建串扰模拟。我认为,最好在PCB上创建一个只有两个驱动器和一个接收器的测试板,其中有两个互连。如果并排走线,则可以使用Sigrity中的仿真工具来计算互连之间的串扰。然后,您可以更改走线之间的距离,走线的宽度以及层堆栈,以确定每个参数如何影响串扰强度。

从仿真中生成理想波形后,就可以继续进行电路板布线了。一旦完成了PCB布局,就可以在关键网络上进行另一轮仿真来完成电路板。两种情况的目的都是为单端和差分网络确定合适的走线密度。在第一轮验证仿真中确定适当的间隙后,您可以将适当的走线间距和差分对间距设置为设计规则,将在布局PCB时遵循这些设计规则。

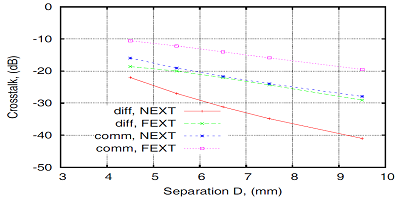

如果您可以准备如下图所示的图形,则在完成布局之前,您已经做了很多艰苦的工作来防止串扰。在该图中,使用了单个极限频率(2 GHz),具有固定的层间隔和走线厚度。随着回路电感的增加,增加层间距将使曲线沿图形向上移动。

串扰与互连间距

在如此简单的图形中总结出EMI可能更加困难,因为您将看到的结果可能是复杂的频率和几何函数。但是,使用正确的仿真工具,您可以检查整个PCB的EMI敏感性和串扰强度。

创建互连信号噪声模拟

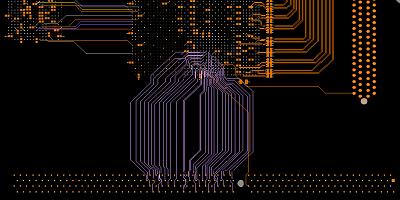

当您进入Allegro Sigrity时,可以从Allegro Sigrity SI主窗口中的Analysis Workflows选项卡访问串扰模拟。下面显示的一组差分对是串扰仿真的主要候选对象。首先,您需要在设置模拟时按名称选择网络。

将您的电路板置于Sigrity中,以进行互连信号噪声仿真

在分析中设置的另一个重要点是将包含在分析中的每个网络周围的区域。如果单击“分析工作流程”选项卡中的“分析选项”条目,则可以使用GeoWindow选项设置每个迹线周围的模拟区域的大小。

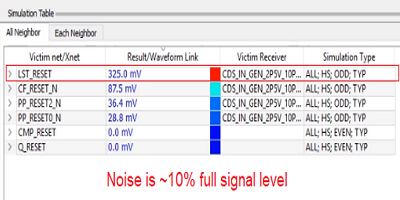

定义设置后,该工具将返回与设计规则进行比较的结果。结果以颜色编码并按降序排列。尽管它们是用颜色编码的,但您也可以看到一个数值结果,以便可以比较由于互连信号噪声引起的峰值过压/欠压,并将其与信令标准进行比较。

LVDS组件在接收器上看到的互连信号噪声耦合(串扰)仿真结果(接收器需要3.3 V差分电压)

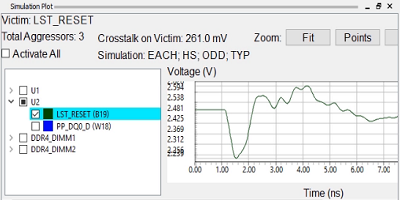

当我们专门查看LST_RESET网络时,我们看到3条侵害者迹线,在该网络上产生串扰

在受害迹线上互连信号噪声图

在该网络中,解决方案是修改受害者迹线和攻击者迹线之间的间隔。由于产生此级别的互连信号噪声涉及3条走线,因此难以确定最佳走线布置。将受害迹线移离一个攻击者可能需要将其移近其他攻击者之一。在这种情况下,您应该试验不同的布置,然后重新运行仿真以确定最小化串扰的布置。

您可以在Allegro Sigrity SI的“分析工作流程”选项卡中访问其他重要的模拟:

阻抗工作流程:检查由于共模或差模驱动下的耦合而引起的阻抗不连续和沿走线的变化。

耦合工作流程:提取不同网络之间的耦合系数,这将决定偶数和奇数模式阻抗。

反射工作流程:检查由于较小的阻抗不匹配而引起的来自接收器的反射。

返回路径工作流程:检查单端网络中信号的返回路径。