24小时联系电话:18217114652、13661815404

中文

行业资讯

高速PCB设计中的走线长度匹配

每个电子信号都需要一定的时间才能沿着导体传播并到达目的地。由于电路板上的分散和损耗,在某些情况下需要对高速电路板上的PCB走线长度进行匹配。当您知道如何识别需要长度匹配的电路板部分时,可以采取重要步骤来确保信号按时到达接收器。

如果信号速度和任何迹线长度不匹配之间的联系不明显,则可以将允许的迹线不匹配确定为时间差(对于数字信号)或相位差(对于模拟信号)。PCB走线长度匹配通常以差分对的形式进行讨论,但也适用于具有单端信号的网络和总线以及差分驱动的总线。由于计算机外围设备和其他数字系统需要连续更快的运行速度,因此计算机网络中的传播延迟在承载数字信号的导体中允许的走线长度上设置了严格的公差。以下是在不同类型的系统中应用PCB迹线长度匹配的一些极佳实践。

什么是走线长度匹配?

PCB走线长度匹配恰如其名:在两条或多条PCB走线在板上布线时,您要匹配它们的长度。这些跟踪可能是以下之一:

并行路由的多条单端走线

差分对的每一端

多个并联的差分对,单端或差分对与时钟信号并行布线

数字信号的PCB走线不需要完全匹配长度。在上升沿上总会有一定的抖动,因此并行路由的信号永远不可能完美匹配长度。目的是将长度或时序失配减小到某个极限值以下。允许的长度不匹配和时序不匹配与信号速度有关:

如果您不知道系统中允许的走线长度不匹配,请不要担心。只需检查您的信令标准,接口标准或组件数据表即可。由于计算机外围设备的标准化程度很高,因此大多数组件都使用许多高速信令标准之一,并且您可以在规格中轻松找到路由规格,所需的阻抗和允许的长度不匹配。

长度不匹配也可以使用信号速度转换为定时不匹配,尽管在选择数字信号的速度时要格外小心。这是因为通常以小于1 ns的边沿速率运行的现代数字信号将具有高达GHz的带宽,并且只能容忍非常小的失配。PCB基板中的分散会导致信号速度随频率变化。例如,FR4在〜1 GHz以下具有正常色散,因此较低的频率比较高的频率更早到达接收器。

迹线长度匹配的目标是防止并行数据总线上的时滞。偏斜只是指两个或多个数字信号的上升沿之间的时序不匹配。在并行总线中,在最短走线上传播的信号将最早到达,因此它将在总线上的其他信号之前触发下游门。行业标准的PCB设计软件将允许您在原理图中定义总线和差分对,但您需要在布局中强制使用迹线长度匹配,以使偏斜度在允许的范围内。

偏斜和走线长度匹配

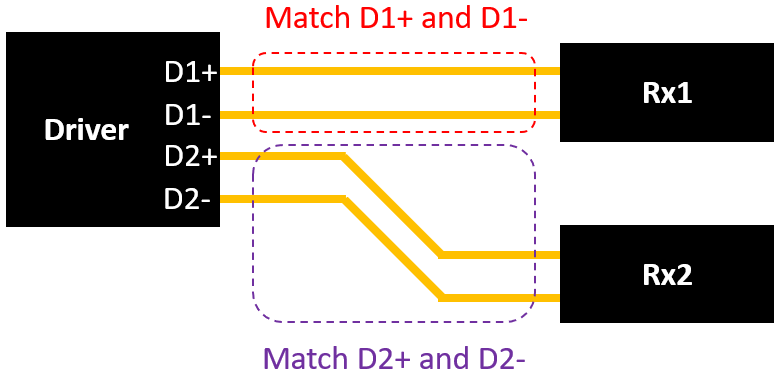

多个单端网络中的长度匹配非常简单;只需添加调整结构,以确保总线上的所有走线都具有相同的长度。调整结构将在下面更详细地讨论。对于差分对,单个差分对的每一端应长度匹配。下图显示了将PCB迹线长度匹配应用于差分对的示例。

上面显示的差分对在单个驱动器(例如,FPGA)和两个不同的接收器之间路由。每个接收器分别读取D1和D2上的差分信号。在此,差分对D1的每一端都需要进行长度匹配。类似地,差分对D2的每一端都需要长度匹配。但是, D1和D2不需要彼此匹配,因为它们没有并行传输数据。这些差分对中的每对一次只传送一个比特,我们只需要进行长度匹配以确保在每对中消除共模噪声。

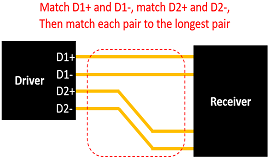

如果您有多个差分对携带并行数据,则每个差分对都需要匹配,然后这些对必须彼此匹配。如下所示,其中单个驱动程序正在将并行数据发送到单个接收器。这样可确保每个差分对都能充分消除共模噪声,并确保接收并行数据而不会出现位之间的偏差。

时钟信号

下一个自然要问的问题与时钟信号有关:来自系统时钟的信号应如何在具有多个链IC的整个数字系统中进行长度匹配?在上面的示例中,时钟信号需要来自某个地方,以便接收器锁存。答案是:在此拓扑中不使用系统时钟信号!

在大型数字系统中,使用系统时钟来触发组件链中的每个IC极为困难。这是因为每个IC可能具有不同的逻辑门延迟,上升时间和总体信令标准。因此,现代数字组件使用源同步时钟或嵌入式时钟。在前者中,时钟信号与并行数据迹线一起在一条迹线中路由,并且该时钟迹线需要与其他数据迹线长度匹配。

在嵌入式时钟的情况下,没有时钟跟踪。嵌入式时钟用于串行通信(例如,SerDes通道),而时钟信号被编码为串行数据流中的前几个位。如果您要设计带有差分对(例如LVDS)的SerDes通道,则仍需要使用上述技术对差分对进行长度匹配。

长度调整结构

存在三种常见的PCB走线长度调整结构,每种结构都可以在其自己的文章中进行讨论。这些结构的其他一些名称是切回路由和蛇形路由。这些不同的结构中的每一个都会对传输线阻抗和FEXT产生一些有趣的影响

如果您要对匹配的差分对组进行长度匹配,那么每一个都是延长差分对的好选择。无论本结构如何应用,都应尝试使长度调整部分保持对称,如果结构缺乏对称性,共模噪声仍将被充分消除。

当逃避过孔或长度不匹配很短时,应尝试将这些结构之一应用于网络的源端,而不是接收器端。如果在接收器端应用该结构,则可能无法充分消除轨迹中较早接收到的任何共模噪声。对于过孔附近的短失配,可以在源端施加一个小的延迟(称为相位匹配)。

模拟差分信号呢?

上面讨论的思想适用于数字信号,但是模拟信号也可以作为差分对进行路由。即使在非常高的频率下,这在许多系统中也很少见。但是,可以使用差分运算放大器将模拟信号作为差分对进行路由。像德州仪器(TI)这样的公司提供高带宽(〜GHz带宽)差分运算放大器组件,非常适合路由模拟差分对。使用这些组件,您可以轻松地将模拟信号路由到电路板上,并且当需要与单端模拟IC接口时,可以转换回单端模拟信号。

模拟差分信号需要精确的长度匹配,就像数字差分信号一样。区别在于模拟差分信号类似于三相AC布线,其中相邻的模拟接地层用作该对两端的参考。尽管数字信号显然不需要接地层,但出于上述原因,将接地层放置在数字差分对附近是有利的。

上面显示的PCB迹线长度匹配准则也需要与模拟差分对一起使用,因为它们会累积偏斜,就像差分信号一样。它们还需要非常精确的相位匹配,并且容易受到相位噪声的影响。用于最小化抖动的相同PDN设计要点也适用于防止相位噪声的模拟组件。但是,幸运的是,在设计模拟PDN时,您正在以较小的带宽工作,这使得将模拟PDN阻抗最小化变得容易得多。