24小时联系电话:18217114652、13661815404

中文

技术专题

设计电路板加速测试(FOAT)应用于PCB DFR

设计电路板以提高可靠性时,最好遵循更合理的做法。尽管大多数电路板设计人员可能认为他们的设计是完美无瑕的,但是风险管理通常需要在现场对电路板性能进行一次评估,结果表明某些电路板会过早失效。因此,逻辑指示该设计电路板应遵循可靠性步骤。例如可靠性工程师采取的措施,将被并入您的电路板的开发过程中。

首先,让我们看一下设备可靠性以及设计电路板人员在实现该目标或可靠性设计(DFR)中的作用。然后,我们将探索如何使用统计故障率(SFR)分析方法,面向故障的加速测试(FOAT)来指导我们的DFR努力,不仅提高可靠性,而且优化电路板开发流程的效率。

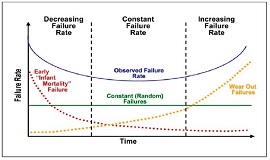

电子设备故障率曲线

设计PCBA的可靠性

现场观察到的故障是衡量电路板可靠性的极好的精确指标。对于风险管理,这种实际结果被用作催化剂,以不断更新PCBA开发流程。但是,这种不断发展的可靠性策略并不是最有效的,因为它的成功取决于发生的足够多的失败,从而可以识别风险因素并设计出有效的控制措施来减轻它们。能够在部署电路板之前预测故障率会更好。

在部署之前评估PCBA可靠性的最常用方法是测试。电路板测试的类型很多。有些是非侵入性的,可以通过手动或自动光学检查(AOI)来完成。其他在线测试(ICT);例如飞针(如下图所示)和测试元件和电路功能的钉床有助于评估可靠性,但需要包括设计步骤以方便在制造过程中使用。

飞针PCBA测试

例如,指甲床测试需要对要测试的产品进行规格说明,并需要专门的测试设备,这会延长制造周期。还有破坏性的测试技术。例如高加速寿命测试(HALT)和比较跟踪指数(CTI)测试,可用于确定电路板在物理损坏之前可以承受的压力量。

毫无疑问,可以使用测试来量化电路板在现场何时以及是否会失败。缺点是大多数测试方法都有相关的成本。包括无法使用的电路板和时间延迟,这使它们无法有效地确定电路板设计的可靠性。为了帮助解决该问题,可以进行可靠性(DFR)仿真和FEA分析设计。例如EMC / EMI,电源完整性(PI),信号完整性和热评估。但是,在大多数情况下,可靠性是主要考虑因素,因此必须确保测试的准确性。

如上所示,设备可靠性要求设计者和合同制造商(CM)之间进行协作。因此,DFR涉及执行测试或模拟以及指定物理测试标准。

基于故障导向加速测试(FOAT)的DFR

最近,人们试图通过添加确定是否确实需要物理测试(尤其是昂贵的破坏性类型)的逻辑方法来提高DFR的效率。为了证明没有必要进行此测试,需要使用另一种量化故障率的方法。这包括准确估计随机统计故障率(SFR)的能力,该统计故障率构成了上面图2中生命周期曲线的恒定故障率部分。出现的一种方法是面向故障的加速测试(FOAT)。

FOAT构成概率方法进行可靠性或PDFR设计的基础或基础,并且具有以下属性:

基于故障导向的加速测试(FOAT)的DFR

利用物理建模

无需物理测试即可量化故障率

比物理测试更具成本效益

允许一系列条件

除了上面列出的优点外,FOAT还可用于确定是否执行物理测试。尽管计算量很大,但是可以使用功能强大的数学建模软件来执行FOAT,与物理测试方法相比,它可以节省时间和成本。