24小时联系电话:18217114652、13661815404

中文

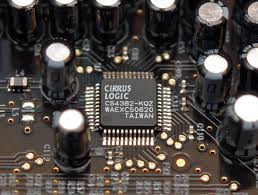

电子资讯

集成电路设计ESD保护

根据ESD协会的统计,“由于未知原因”损坏的所有电子产品中有25%归因于ESD。这些损失估计使电子行业每年损失300亿人民币。因此集成电路设计中必须要考虑到ESD保护。

什么是ESD?是什么导致现象?

ESD是静止时释放的电荷(静电)。这主要是由停留在特定表面或环境空气中的电子失衡造成的。由电子的缺乏或过剩引起的电子不平衡会导致电场,该电场能够远距离影响其他物体。

ESD也指的是当两个带相反电荷的物体相互接触时发生的情况。如果这两个物体距离足够近,则会释放电压,产生电压尖峰,并产生电磁场。

ESD保护的重要性

ESD故障是集成电路(IC)和其他电子系统具挑战性的可靠性问题之一。实际上,行业统计数据表明,超过30%的IC故障是由ESD或电过载(EOS)事件引起的,每年给行业造成上百亿的损失。

但是,知道存在问题和实现问题的解决方案并不是相互排斥的。此外,当前的解决方案不是万金油的解决方案。尽管这些EMI(电磁干扰)确实可能给电子系统带来同等程度的危险,但他们产生的原因不一。

众所周知,所有IC和其他电子产品都需要ESD保护。但是,并非每种预防措施对于遇到的每种ESD模型都同样有效。在接下来的几段中,我将进一步阐述它们所构成的不同模型和保护问题。正如我之前所避免的那样,这也将进一步说明,不保证一种尺寸适合所有方法。

ESD应力模型的类型

ESD可能在各种情况下发生。为了更好地解决这些问题,这些ESD应力模型已分为三种特定类型或模型。ESD应力模型的三种类型是人体模型(HBM),机器模型(MM)和带电设备模型(CDM)(CDM)。

这三个基本模型在行业中用于测量IC的ESD保护水平,并评估ESD应力在不同情况下的影响。

人体模型

顾名思义,HBM表示由ESD现象引起的ESD应力,该现象在带静电的人体接触芯片并形成放电路径时发生。

机器模型

这种现象是由带电的带电荷的机器或工具与芯片接触并在生产线上形成向地面的放电路径时发生的现象引起的。

带电设备模型

生产或运输过程中对IC(集成芯片)进行充电的场景。此外,在IC与任何导体或地面接触之后,电荷在IC内部和外部之间发生转移。

CMOS技术在集成电路设计中的应用

CMOS技术中的集成电路需要静电放电(ESD)保护设计。CMOS技术中的ESD保护器件的选择包括二极管,MOSFET和可控硅整流器(SCR)。

但是,这些ESD保护设备具有一些不良的副作用。简而言之,由于寄生电容,它们会在高频输入/输出(I / O)焊盘上引起信号损耗。因此,为了使这些ESD保护电路对高频性能的影响最小,必须仔细设计I / O焊盘上的ESD保护电路。

一旦能够减小寄生电容,就可以轻松地将ESD保护电路与高频电路组合或共同设计。随着高频电路工作频率的增加,针对高频应用的片上ESD保护设计将持续成为重要的设计因素。

CDM集成电路设计ESD保护

近年来,随着自动机械和设备在生产线上的普遍使用,CDM已被证明是所有ESD应力模型中具破坏性的放电机制。就ESD保护设计而言,CDM已逐渐成为最重要的问题。

CDM的最重要特征之一是低阻抗放电路径,这导致了极快的电荷转移。这个特殊的属性使CDM在CMOS技术的ESD保护设计中成为关注点。这就是为什么在CDM放电期间,上升时间非常短(通常为0.25-0.75ns)的原因,这需要较短的CDM ESD保护设计触发时间。

另外,随着芯片集成技术的改进和新封装技术的发展,芯片的等效寄生电容增加。因此,导致芯片所携带的电荷量增加,并且这需要CDM ESD保护设计的保护能力得到提高。

总之,不能夸大CMOS技术中IC的ESD保护设计的重要性。随着IC在应用和功能方面的不断发展和功能不断增强,很明显,集成电路设计ESD保护也必须发展。