24小时联系电话:18217114652、13661815404

中文

行业资讯

接口芯片8255的扩展方法

一般而言,可编程接口芯片具有存储器和地址线 。所谓可编程,是指CPU通过一条指令将一定的数据写入接口芯片的某个存储器中,接口芯片在接收到CPU发送的数据后自动转换数据。然后执行数据代表的动作

不同的CPU对接口芯片的处理方式不同。一些CPU处理接口芯片的内存与CPU本身使用的内存不同。接口芯片内存的操作称为I / O操作,内存本身的操作用于CPU本身。这称为内存操作,并且I / O操作和内存操作使用不同的指令。这称为I / O端口的独立寻址。

此方法的优点是I / O端口不占用内存的地址空间,并且内存空间和I / O空间是独立的。缺点是在CPU中单独设置了I / O端口访问指令,并且增加了CPU的复杂性。INTEL的8086系列采用了这种结构。

另一种处理方式是将接口芯片 的存储器视为外部数据存储器,而无需单独设置I / O端口的访问指令。此方法称为统一寻址,而8051采用此方法。

下面我们介绍接口芯片8255。

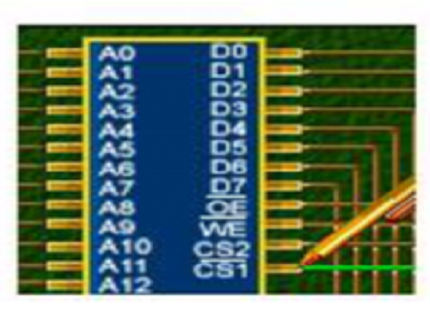

8255是并行接口扩展芯片。它具有一个要扩展的8位并行接口D0-D7,以及三个扩展的8位并行接口PA,PB,PC。通过其两条地址线AO,A1选择四个存储器,即PA端口存储器,PB端口存储器,PC端口存储器和控制端口存储器。

当A1A0为00时,8255将D0-D7连接到PA。

当A1A0为01时,8255将D0-D7连接到PB。

当A1A0为10时,8255将D0-D7连接到PC。

当A1A0为11时,8255将D0-D7连接到内部控制寄存器。

假设将两个8K数据存储器和一个8255混合并扩展到CPU的外部数据存储器中,并且它们的片选信号以解码方式连接。

解码器74139的输入连接到CPU的P2.5和P2.6。

当P2.6和P2.5是00,该解码器输出端子YO是有效的,并且数据的第一片存储器中选择 。可以看出,第一片存储器的逻辑地址为0000H-1FFFH和8000H-9FFFFH,每个物理单元有两个逻辑地址

当P2.6和P2.5为01时,解码器输出Y1有效,选择第二条存储器,第二条存储器的地址为2000H-3FFFH和0AOOOH-OBFFFH。

当P2.6和P2.5为10时,解码器输出Y2有效。选择8255时,8255的逻辑地址为4000H-5FFFH和0C000H-0DFFFH。

当P2.6和P2.5为11时,解码器输出Y3有效,并且未选择任何存储器,即,在这种情况下的地址是无效地址,包括6000H-7FFFH和0E000H-OFFFFH。