24小时联系电话:18217114652、13661815404

中文

技术专题

如何对高速PCB设计信号进行相位噪声测量

PCB中有很多噪声源,而相位噪声可能是很难固定在实际板上的噪声源之一。如果要调试具有高BER的高速电路板,则可能需要从出现故障的电路板部分或时钟中收集相位噪声测量值。

不必太深入系统的IC端,相位噪声可能就是您正在使用的组件的固有属性,例如SerDes组件内部的PLL。在其他情况下,电路板中的其他组件,布局甚至基板都会造成随机信号倾斜。当此抖动的来源不明显时,您将想要收集可疑组件的相位噪声测量值,既可以作为单独的DUT,也可以在可疑板上使用。

什么是相位噪声和抖动?

大多数数字设计人员使用术语“抖动”来指代定时噪声,其中在互连上发射信号的时间有所不同。模拟设计师更可能使用术语“相位噪声”,这意味着模拟信号与其参考噪声之间的相位差会随机变化。这些术语相互关联并且指的是同一件事:时域(抖动)或频域(相位噪声)中信号时序的变化。

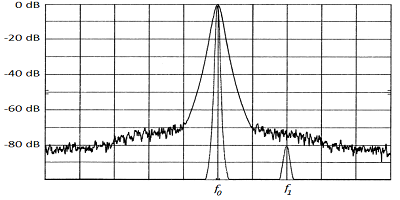

在频域中,相位噪声测量可能类似于下图所示。在此,以f0的载波频率发出信号,而在f1处以较弱的频率发出信号。f0上存在相位噪声会有效地增加信号的带宽并提高本底噪声。如果f1处的信号足够弱,则该信号将隐藏在f0的相位噪声之后。

频域中的示例相位噪声测量

抖动是在时域中看到的相位噪声的表现。抖动可以直接在眼图中看到,并且易于识别。通常,RMS抖动是用于量化可接受的BER值的重要参数是什么促使需要进行相位噪声测量?如果您使用的是数字系统,并且在眼图中发现抖动,则需要确定会导致设备抖动的最强相位噪声源。诊断模拟信号的相位噪声就像将额定带宽与测量的带宽进行比较一样简单。

上面的最后一点表示可以预期在系统中看到的相位噪声的下限。如果相位噪声似乎是一个问题,请检查数据表中的时钟/参考振荡器。如果固有的振荡器噪声占您测得的相位噪声的大部分,那么您可能只需要一个更稳定的振荡器/ PLL。

可以使用带有近场探头的频谱分析仪直接从板上采集相位噪声测量值。相位噪声也可以通过使用测试夹具连接到DUT的频谱分析仪进行测量(确保对连接器的S参数进行去嵌入)。在这里,您正在测量功率谱密度,因此,您测量的相位噪声是测量带宽的函数。公认的标准是在1 Hz带宽内收集连续的测量值。

在解释相位噪声测量值时,您的目标是确定最突出的噪声源,并逐步减少它们。产生抖动的四种常见相位噪声源是:

噪声从开关模式电源耦合到数据流或系统时钟。

热噪声:在较高温度下,相位噪声会更大。散粒噪声和1 / f噪声也很重要。

基板介电常数的较大变化。通过使用具有更紧密纤维编织的基材来解决此问题。

参考振荡器固有的相位噪声,或系统时钟固有的抖动。在带有PLL的超快速系统中,通常会减少这些误差。

这里的目标是确定最主要的相位噪声源,并首先将其降低。如果这使您的系统符合规范,请考虑完成您的工作。无论您的时钟/参考振荡器的Q值是多少,系统中总会有一定的相位噪声。但是,如果您可以在规格范围内获得BER值或其他性能要求,那么您就可以成功完成工作。

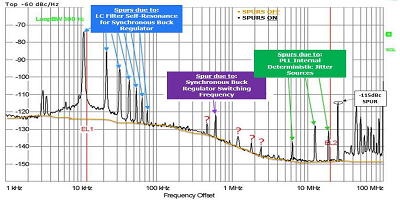

您可以在相位噪声图中直观地发现罪魁祸首,并将其与电路板上的已知噪声源进行比较。下面显示了带有多个相位噪声杂散的示例测量。

相位噪声测量数据[图像源

请注意,上图中的强烈毛刺是由多种原因引起的。可以将上述噪声与电路板上相关组件的参考规格进行比较。可以通过以-10 dBc / Hz的斜率穿过相位噪声规范点来画一条线来完成。超过此线的噪声频谱的任何部分都将落在允许的相位噪声容限之外,并且需要在设计中加以抑制。

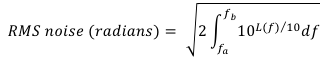

可以使用以下公式根据RMS相位抖动值来量化可接受的相位噪声电平。请注意,L(f)是对数相位噪声数据,因此10的奇数因子出现在积分中,以将其转换回线性数据集。此处的积分取自相关信号范围。

根据数据计算出的RMS相位噪声