24小时联系电话:18217114652、13661815404

中文

技术专题

电路设计PDN管理阻抗

PDN阻抗是高速PCB中的关键概念之一,但许多电路设计人员将其保留为事后考虑。对于以5 V或3.3 V运行的组件,如果在关键组件上使用相邻的平面层和几个去耦/旁路电容器,通常会很好。对于以快速边沿速率运行的设计,以及在PDN中吸收大电流时,您需要仔细设计PDN以抑制大的瞬变。

什么是PDN阻抗管理?

目标PDN阻抗为整个PDN中的峰值阻抗值设置了上限。实际的PDN阻抗将决定电源总线上任何瞬态纹波波形的幅度,这将转化为高速IC的输出信号上的抖动。当IC切换时,它将从电源汲取一些电流,该电流将作为脉冲波形传播通过PDN。PDN中的寄生电容和任何电容器都会提供一定的电抗,从而在PDN中产生瞬态响应。PDN阻抗管理的目标是使任何瞬态波形都尽可能小。

PDN上任何瞬态纹波波形的大小都是PDN阻抗和IC切换时汲取的瞬态电流的函数。由于阻抗是频率的函数,因此需要确保整个相关信号带宽内的整个阻抗曲线都低于某个目标值。两者之间的关系源自欧姆定律

计算您的PDN阻抗目标

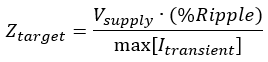

目标PDN阻抗会在整个信号带宽内设置峰值阻抗值的上限。由于组件的电源电压随时间下降,因此允许的电源电压纹波值也随之降低。这些纹波值通常以百分比形式指定,您需要将该纹波百分比转换为阻抗目标。可以使用以下公式计算:

目标PDN阻抗方程式

注意,在上式中,波纹百分比表示为峰峰值,而不是波纹幅度。这是因为纹波不是纯粹的正弦波,因此就振幅而言写纹波没有多大意义。上式的一种形式使用纹波幅度(假设正弦纹波波形),并且分母中放置了50%的因数。注意,用两个方程式计算的目标阻抗值相等。

例如,假设我们使用的电源电压为3.3 V,允许的纹波为2%(峰峰值)。如果集成电路在开关期间可吸收的最大峰值电流为0.5 A,则目标阻抗为132 mOhm。注意,这是一个数量级;PDN可以具有电阻性和电抗性分量,这些分量将共同确定任何纹波波形的幅度。

当您在PDN上的多个设备同时切换的情况下工作时,您需要考虑在任何给定时刻可以汲取的总电流。由于在任何时刻汲取的总电流都将大于单个IC汲取的电流,因此这会将目标PDN阻抗推至更低的水平。

在电路仿真中检查的PDN元素

电路仿真是开始检查和管理PDN阻抗的第一个地方。由于阻抗随频率变化,因此管理PDN阻抗的目标是计算从DC到非常高的频率的阻抗谱。PDN阻抗应覆盖组件的相关信号带宽。这需要在电路仿真中考虑以下几点:

电容器自谐振:由于其等效串联电阻(ESR)和等效串联电感(ESL),任何组件上的去耦/旁路电容器都具有一定的自谐振频率。您可以通过查看数据表从所需的电容器中获得典型值。您的数据表通常还会显示自谐振频率。

平面间电容:您的电路板叠层将确定PDN中电源层和接地层之间的电容。尽管有必要确保高速PCB中的PDN具有足够的去耦,但这是一种寄生效应。通过利用堆叠中的自然电容,可以减少对分立去耦/旁路电容器的依赖。典型值为〜0.5 pF / sq。mm为标准厚度的6层PCB。

重要的是要了解电路仿真不会告诉您某些事情。尽管应始终包括电容器(ESR和ESL)中的寄生效应,但您不能直接考虑平面间电容或其他寄生效应。取而代之的是,您需要在原理图中将任何寄生效应都视为等效电路元件。这需要通过电感和平面环路电感估算平面电容。