24小时联系电话:18217114652、13661815404

中文

技术专题

单端开关与差分信号

如今,当您谈论高速PCB设计时,几乎在您看到的每个地方,产品所需的信号默认都是差分信号。但是,差分信号并不总是处于产品开发的最前沿。移动数据的原始方法是单端信令。而且,在某些情况下,它今天仍在使用。本文将描述单端和差分信号之间的区别,哪些逻辑系列具有单端信号,哪些逻辑具有差分信号,当前数据路径需求,以及即将出现的变化。

单端交换特别地是指由驱动器和传输线组成的数据路径,该传输器在平面上或在一对平面与一个或多个负载输入之间传播。您可以决定何时上升或下降沿经过阈值电压的任何时候发生逻辑状态变化。

采用单端信号传输,如果要精确的时序,上升时间必须非常快。当您通过阈值电压时,精确检测逻辑状态变化的能力取决于上升时间的快慢。

单端信令是发送逻辑信号的最便宜的方法,因为它对每个数据路径只需要一根导线和一个信号引脚,所有数据路径共享相同的“接地”平面。

BTL

CMOS

TTL

低压CMOS

预期信用损失

GTL

左心室TTL

SSTL

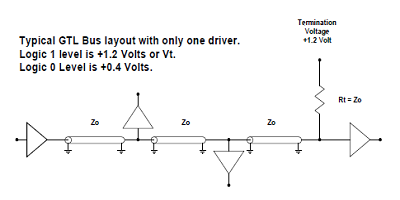

图1描绘了BTL逻辑系列的单端数据路径。当CMOS成为首选逻辑系列时,开发了BTL逻辑系列以替代ECL。它用于驱动大型数据总线。

图1.单端信号数据路径

对于所有上述逻辑系列,信号在两端以及中间负载处均参考信号所经过的平面。在大多数情况下,飞机是逻辑接地,但这不是强制性的。注入连接信号路径元件的接地路径的任何噪声都会腐蚀出现在逻辑输入端的逻辑电平。影响电流电平的常见噪声类型是接地结构中发生的DC和AC压降,因为电流通过该路径流回VDD。当逻辑电平从0切换到1并通过IC的电源线返回给逻辑线充电和放电所需的电流时,也会产生接地反弹。在大多数逻辑上,电源上的这种噪声是EMI的主要来源。

特别是,发生的事情是,对传输线和逻辑器件的输入的寄生电容进行充电和放电所需的电流成为Vdd上“纹波”的主要来源,而Vdd和接地反弹。注意:纹波是电源Vcc或Vdd轨上出现的电压变化。这些变化可以通过电源本身或通过改变导致电源电压下降的负载电流来产生。

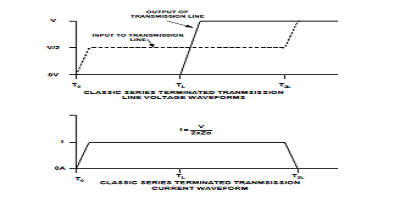

前述电流瞬变限制了可用于数据总线的实际宽度。图2说明了当逻辑线路从逻辑0切换到逻辑1时,在串联终端的传输线路中发生的电流。

图2.串联终端传输线的电压和电流波形

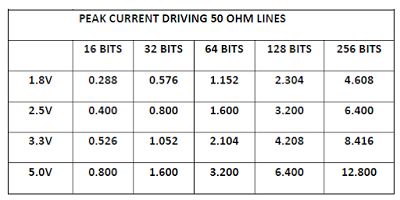

可以为任何逻辑系列计算图2所示的电流。例如,如果逻辑系列为3.3V CMOS,则每条线的峰值电流约为33 mA。如果使用这种逻辑形式创建数据总线,则当所有位同时从0转换到1时,总线所需的峰值电流为总线中位数的33 mA倍。表1列出了几个逻辑系列的峰值电流(以安培为单位,在各种总线宽度下)。

表1.当所有线路从0变为1时,各种宽度数据总线的峰值电流

这些电流必须由电源系统提供。当逻辑线从逻辑0切换到逻辑1时,该电流必须流经IC封装引线的电感。当逻辑线从逻辑1切换到0时,传输线的寄生电容必须通过IC封装的接地引线的电感放电。这就是两种不想要的噪声,即Vdd和接地反弹和纹波的产生位置。

这些噪声源变得如此之大,以至于不再可能制造出具有足够低电感的封装以及功率子系统具有足够高品质的电容来容纳此类噪声。” “这就是导致使用差分信号的原因。”

归根结底,单端开关的主要优点是价格便宜。它的使用已被差分信号取代。我曾经尝试预测单端信令何时会消失,但是仍然可以在DDR内存中找到,所以我不再做那些猜测了。

差分信号

差分信号是一个广泛的话题,涉及许多因素。出于讨论的目的,差分信令的主要好处是它具有应付数据路径两端之间大量接地偏移的能力。注意:术语差分信令和串行信令可互换使用。

“使用差分信号时,您有两条电线,它们的信号相等且相反。当两个波形交叉时,数据位发生变化。因此,对于给定的数据速率,差分信号的边缘不必像单端那样快。”

最初,反对差分信令的情况就是代价。与单端信令相反,在差分信令中,每个数据路径需要两条线,两个连接器引脚,两个驱动器和两个接收器。当数据速率相对较低并且信号路径的两端都在同一接地平面上时,就不需要承担更高的差分信令成本。当单端数据路径变得非常宽且信号的上升沿和下降沿变得非常快时,所产生的开关噪声将使其难以达到噪声目标。

表2列出了几种类型的差分信令协议。所有这些都是为了应付上述数据路径两端之间的接地偏移而创建的。

ECL

LVDS

双相TTL时钟树

以太网链接

RS-422

HDMI

PCIExpress

Infinband

表2.几种差分信令协议

“通常,我们将并行总线转换为串行比特流。最初的PCI总线配置是137个带时钟的单端线。使用PCI Express,我可以用两对差分来代替,每对都可以。这带来了三个好处-我不需要超快速的上升时间,电源上没有SSN,并且需要更少的电线来发送相同数量的数据。”

“使用差分信号,一方面,您必须获取并行数据流,并将其转换为串行(串行器)。另一方面,您必须将数据流从串行传输到并行(解串器)。” “执行此操作所需的逻辑过去非常昂贵。结果,我们仅在遇到严重偏移问题时才使用差分信令。在当今拥有数十亿个晶体管的逻辑的情况下,串行器和解串器基本上是免费的,我们正在将并行总线转换为串行总线。使用现代串行链接,我们将时钟嵌入到数据中,因此不再需要将时钟与数据匹配的艰巨任务。您可以用这些东西构建带宽令人难以置信的系统。”